# **Detector Support Group**

Weekly Report, 2019-10-16

## **Summary**

### Hall A - SoLID Cleo II Magnet

Generating spreadsheet for control systems networking and PLC chassis layouts with module specifications.

#### Hall A – Super BigBite HCAL

• 95% of 1888 cables completed

#### Hall B - Magnets' LV Chassis

- Adding 25.5-µs delay to DAC initialization code in FPGA resolved DAC communication issues.

- **★** Delay allows Cyclone V on DE0-Nano-SoC to run existing LV Chassis FPGA program.

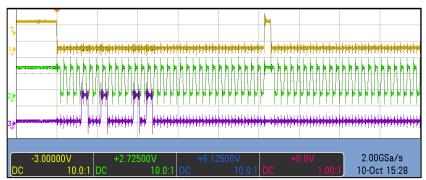

Oscilloscope output for Cyclone V FGPA showing correct DAC initialization with 25.5-µs delay.

#### Hall B - RICH

- Debugged and tested cooling system's compressors.

- \* Leak at fitting of buffer tank supply hose found and repaired.

- **★** Drive belts checked and tightened on Compressor 1.

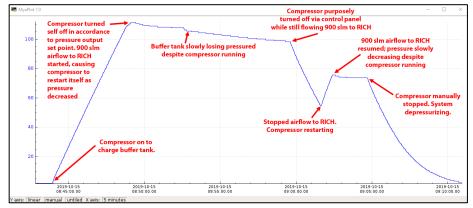

- Compressor 1 cannot maintain set pressure (~110 psi) when flowing 900 slm to RICH.

- If no airflow to RICH, compressor builds buffer tank pressure to set point.

- With airflow, buffer tank pressure slowly decreases despite compressor running.

- \* Compressor 2 behaves as expected and maintains pressure in buffer tank within compressor's internally set output range.

Buffer tank pressure during test of Compressor 1 where it was found compressor does not maintain pressure in buffer tank with 900 slm flow to RICH.

# **Detector Support Group**

Weekly Report, 2019-10-16

- Developed Python program to analyze Compressor 2 start-stop timing from October 9, 2019 at 10:28AM to October 10 at 9:59AM:

- \* Average cycle time:  $23.62 \pm 1.76$  minutes

- \* Average time on during a cycle:  $20.89 \pm 1.66$  minutes

- \* Average time off during a cycle:  $2.73 \pm 0.54$  minutes

- **★** Duty cycle: 88.44%

### **Engineering Division**

• Soldered 240 capacitors on to beam position monitor PCBs

#### DSG R&D – EPICS Archiver

- Wrote shell script to monitor and log data for multiple PVs into text file

- Created MySQL database to archive PV information

#### DSG R&D – Analysis Package for Hardware Interlock Data

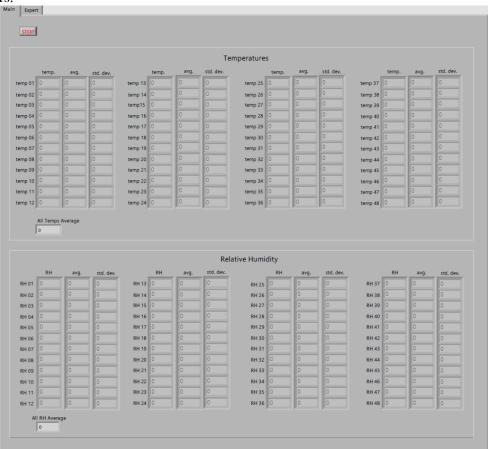

Added average and standard deviation calculation for all relative humidity and temperature sensors.

Front panel of LabVIEW program with average and standard deviation displayed with raw data.